臺積電引領先進封裝技術革新,CoPoS試產線啓動

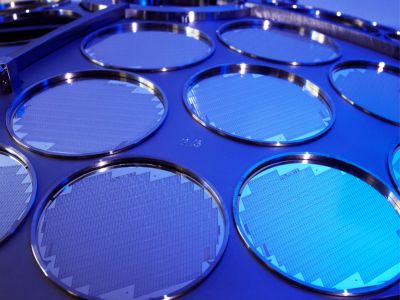

華爾街金融巨頭摩根士丹利發佈研報指出,臺積電已啓動建設310 mm² Panel-Level chiplet先進封裝試產線,即CoPoS先進封裝體系,標誌着“圓片級CoWoS向面板級CoPoS先進封裝”的封裝技術迭代正式進入投資與初步試製造期。

臺積電的CoPoS試產線將推動芯片產業鏈的“先進封裝大變革”,主要用於解決CoWoS先進封裝產能瓶頸和成本問題,面向下一代AI訓練/推理AI GPU/AI ASIC,追求更大規模的chiplet芯粒和更高HBM堆疊數,以實現性能提升並降低成本。

| 封裝技術 | 特點 | 應用 |

|---|---|---|

| CoWoS | 圓片級封裝,受限於圓片面積 | AI GPU |

| CoPoS | 面板級封裝,面積更大,性能提升 | 下一代AI芯片 |

CoPoS技術優勢與市場影響

CoPoS先進封裝體系借鑑CoWoS的硅插硅技術棧,但在基板形態、高端半導體設備鏈與良率瓶頸上做了系統級調整,用更強勁的性能天花板以及更易於擴張的產能,更大範圍滿足全球AI算力需求。

對英偉達、AMD等AI/HPC超級客戶而言,CoPoS提供更大規模的先進封裝I/O與HBM堆疊數,极大程度缓解先进封装产能供不应求與初步流片、芯片製造成本高企。

從業績增長與估值擴張角度來看,整個芯片產業鏈有望迎來大舉增長。對於英偉達、AMD以及三大EDA巨頭來說,有望通過供給側產品更新迭代推動更大規模終端需求,尤其對於AI芯片霸主英偉達來說有望更大程度滿足AI算力需求;半導體高端設備與芯片原材料鏈因CoPoS面板化則即將迎來新一輪超大規模設備資本支出。

CoPoS與AI算力需求

隨着ChatGPT等AI技術的發展,AI算力需求呈指數級增長。CoPoS通過把承載面積放大到典型的310 × 310 mm,可容納多達10-12顆下一代HBM——HBM4與更多chiplet芯粒,理論峯值帶寬有望突破13-15 TB/s,存儲容量至少翻倍。

CoPoS提供的寬廣得多的“性能上限”,更大範圍滿足算力需求。當AI算力需求以及AI模型的參數規模繼續爆炸式增長,CoPoS先進封裝將全面釋放出面板面積優勢,帶來更大規模的AI芯片等AI算力基礎設施性能提升以及單位算力成本下降。