台积电引领先进封装技术革新,CoPoS试产线启动

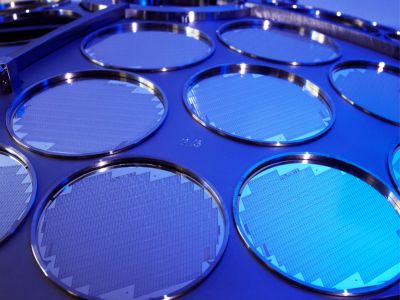

华尔街金融巨头摩根士丹利发布研报指出,台积电已启动建设310 mm² Panel-Level chiplet先进封装试产线,即CoPoS先进封装体系,标志着“圆片级CoWoS向面板级CoPoS先进封装”的封装技术迭代正式进入投资与初步试制造期。

台积电的CoPoS试产线将推动芯片产业链的“先进封装大变革”,主要用于解决CoWoS先进封装产能瓶颈和成本问题,面向下一代AI训练/推理AI GPU/AI ASIC,追求更大规模的chiplet芯粒和更高HBM堆叠数,以实现性能提升并降低成本。

| 封装技术 | 特点 | 应用 |

|---|---|---|

| CoWoS | 圆片级封装,受限于圆片面积 | AI GPU |

| CoPoS | 面板级封装,面积更大,性能提升 | 下一代AI芯片 |

CoPoS技术优势与市场影响

CoPoS先进封装体系借鉴CoWoS的硅插硅技术栈,但在基板形态、高端半导体设备链与良率瓶颈上做了系统级调整,用更强劲的性能天花板以及更易于扩张的产能,更大范围满足全球AI算力需求。

对英伟达、AMD等AI/HPC超级客户而言,CoPoS提供更大规模的先进封装I/O与HBM堆叠数,极大程度缓解先进封装产能供不应求与初步流片、芯片制造成本高企。

从业绩增长与估值扩张角度来看,整个芯片产业链有望迎来大举增长。对于英伟达、AMD以及三大EDA巨头来说,有望通过供给侧产品更新迭代推动更大规模终端需求,尤其对于AI芯片霸主英伟达来说有望更大程度满足AI算力需求;半导体高端设备与芯片原材料链因CoPoS面板化则即将迎来新一轮超大规模设备资本支出。

CoPoS与AI算力需求

随着ChatGPT等AI技术的发展,AI算力需求呈指数级增长。CoPoS通过把承载面积放大到典型的310 × 310 mm,可容纳多达10-12颗下一代HBM——HBM4与更多chiplet芯粒,理论峰值带宽有望突破13-15 TB/s,存储容量至少翻倍。

CoPoS提供的宽广得多的“性能上限”,更大范围满足算力需求。当AI算力需求以及AI模型的参数规模继续爆炸式增长,CoPoS先进封装将全面释放出面板面积优势,带来更大规模的AI芯片等AI算力基础设施性能提升以及单位算力成本下降。